Логический элемент «И-НЕ»

Показана схема на рис. 5 а. Здесь диод Д3 выполняет роль так сказать фильтра во избежание искажения сигнала. Если на вход х1 или х2 не подан сигнал (х1=0 или х2=0), то через диод Д1 или Д2 будет протекать ток. Падение на нем не равно нулю и может оказаться достаточным для открытия транзистора. Последствием чего может стать ложное срабатывание и на выходе вместо единицы мы получим ноль. А если в цепь включить Д3, то на нем упадет значительная часть напряжения открытого на входе диода, и на базу транзистора практически ничего не приходит. Поэтому он будет закрыт, а на выходе будет единица, что и требуется при наличии нуля на каком либо из входов. На рис. 5б и в показаны таблица истинности и схемное обозначение данного устройства.

Рис.5

Логические элементы получили широчайшее применение в электронике и микропроцессорной технике. Многие системы управления строятся с использованием именно этих устройств.

Универсальный триггер

JK-триггер

JK-триггером называют автомат Мура с двумя устойчивыми состояниями и двумя входами J и K, который при условии J * K = 1 осуществляет инверсию предыдущего состояния (т.е. при J*K=1, Q(t+1) = Q(t)), а в остальных случаях функционируют в соответствии с таблицей истинности RS триггера, при этом вход J эквивалентен входу S, а вход K — входу R. Этот триггер уже не имеет запрещенной комбинации входных сигналов и его таблица истинности, то есть зависимость Q(t+1) = f имеет вид:

Таблица истинности JK-триггера:

| J | K | Q(t) | Q(t+1) |

По этой таблице можно построить диаграмму Вейча для Q(t+1), которую можно использовать для минимизации, и матрицу переходов:

| KQ(t) |

| J |

Матрица переходов JK-триггера:

| J | K | Q(t) | Q(t+1) |

| b1 | |||

| b2 | |||

| b3 | |||

| b4 |

| ____ | _ | |||

| Q(t+1) = J* | Q(t) | v | K | *Q(t) |

В интегральной схемотехнике применяются только тактируемые (синхронные) JK триггера, которые при C=0 сохраняют свое состояние, а при C=1 работают как асинхронные JK триггера.

Триггер JK относится к разряду универсальных триггеров, поскольку на его основе путем несложной внешней коммутации можно построить RS-, D— и T— триггера. RS-триггер получается из триггера JK простым наложением ограничения на комбинацию входных сигналов J=K=1, так как эта комбинация является запрещенной для RS триггера.

Счетный триггер на основе JK триггера получается путем объединения входов J и K.

Триггер задержки (D-триггер) строится путем подключения к входу K инвертора, на который подается тот же сигнал, что и на вход J. В этом случае вход J выполняет функцию входа D, а все устройство в целом реализует таблицу переходов D-триггера.

Лекция 6. Структурная схема конечного автомата

В структурной теории автомат представляют в виде композиции двух частей: запоминающей части, состоящей из элементов памяти, и комбинационной части, состоящей из логических элементов:

Комбинационная схема строится на логических элементах, образующих функционально полную систему, а память – на элементарных автоматах, обладающих полной системой переходов и выходов.

Каждое состояние абстрактного автомата ai, где i={0, n}, кодируется в структурных автоматах набором состояний элементов памяти Qi, r={1,R}. Поскольку в качестве элементов памяти используются обычные триггера, то каждое состояние можно закодировать двоичным числом ai = Q1a1Q2a2… Qrar. Здесь аi={0, 1}, a Q – состояние автомата . Отсюда:

| __ | ||

| Qa = | Q | ,еслиa=0 |

| Q | ,еслиa=1 |

Общее число необходимых элементов памяти можно определить из следующего неравенства . Здесь (n+1) – число состояний. Логарифмируя неравенство получим . Здесь ]C [ — означает, что необходимо взять ближайшее целое число, большее или равное C.

В отличии от абстрактного автомата, имеющего один входной и один выходной каналы, на которые поступают сигналы во входном X={x1,x2,…,xm} и выходном Y={y1,y2,…,yk} алфавитах, структурный автомат имеет L входных и Nвыходных каналов. Каждый входной xj и выходной yj сигналы абстрактного автомата могут быть закодированы двоичным набором состояний входных и выходных каналов структурного автомата.

| xi = o1a1 o2a2… oLaL |

| yg = Z1a1Z2a2… ZNaN |

Здесь ofи Zh– состояния входных и выходных каналов соответственно.

Очевидно число каналов L и N можно определить по формулам ; , аналогичным формуле для определения R.

Изменение состояния элементов памяти происходит под действием сигналов U=(U1,U2,…,Ur), поступающих на их входы. Эти сигналы формируются комбинационной схемой II и называются сигналами возбуждения элементарных автоматов. На вход комбинационной схемы II, кроме входного сигнала xj, по цепи обратной связи поступают сигналы Q=(Q1, Q2, …, QR), называемые функцией обратной связи от памяти автомата к комбинационной схеме. Комбинационная схема I служит для формирования выходного сигнала yg, причем в случае автомата Мили на вход этой схемы поступает входной сигнал xj, а в случае автомата Мура – сигнал xj не поступает, так как yg не зависит от xj.

Примеры основных логических элементов

На чипах с логической функцией выполняют основные операции:

- конъюнкция — умножение;

- дизъюнкция — сложение;

- инверсия — отрицание;

- сложение по модулю 2.

Логический элемент «И»

Микросхема «И» выполняет конъюнкцию над входной информацией. Элемент «И» имеет 2-8 входов и один выход.

Пример

Для микросхемы с двумя входами логическая единица на выходе возможна только при подаче на оба входа истинного значения. В иных случаях на выходе получится ноль.

Логический элемент «ИЛИ»

Действие сложения над входными данными выполняет элемент «ИЛИ». У этого устройства может быть 2 и более входов и лишь один выход.

Пример

У элемента «ИЛИ» с двумя входами высокий потенциал на выходе появится при подаче такой же величины на первый или второй вход, а также на оба входа одновременно.

Логический элемент «НЕ»

Операцию отрицания осуществляет элемент «НЕ». Поскольку он имеет по одному входу и выходу, его называют инвертором.

Для элемента «НЕ» характерно обращение входной информации. При подаче на вход логической единицы выйдет логический ноль, и наоборот, при подаче нуля выйдет единица.

Логический элемент «И-НЕ»

«И-НЕ» выполняет функцию отрицания результата конъюнкции. Название следует из принципа работы элемента: «И-НЕ» представляет собой элемент «И», который дополнен элементом «НЕ». Следовательно, «И-НЕ» осуществляет операцию, обратную для элемента «И».

Логический элемент «ИЛИ-НЕ»

Комбинация «ИЛИ-НЕ» выполняет операцию отрицания дизъюнкции. Данный элемент является противоположным элементу «ИЛИ», соответственно, значения входа и выхода для этих элементов тоже будут обратными друг другу.

Логический элемент «исключающий ИЛИ»

Элемент с функцией сложения по модулю 2 называется «исключающем ИЛИ», другое его название — «неравнозначность». Данная микросхема имеет два входа и один выход.

Истинное значение будет в случае разных сигналов на входах. Если на обоих входах будет высокий потенциал, на выходе получится низкий. При одновременной подаче низкого уровня сигнала на каждый вход на выходе также будет низкий уровень.

Где применяются логические элементы

Логические элементы могут служить автономными частями схемы и составными частями более сложной схемы. В качестве самостоятельного элемента микросхему используют для управления устройством. Также чип с логической опцией имеет назначение генератора импульсов в радиодеталях.

Осторожно! Если преподаватель обнаружит плагиат в работе, не избежать крупных проблем (вплоть до отчисления). Если нет возможности написать самому, закажите тут

В комбинационных цифровых схемах рассматриваемые элементы составляют часть больших и сверхбольших интегральных схем, шифраторов и дешифраторов. В триггерах, регистрах, счетчиках и других схемах с памятью также применяют микросхемы с функцией логических действий.

Трехразрядный реверсивный счетчик с последовательным переносом

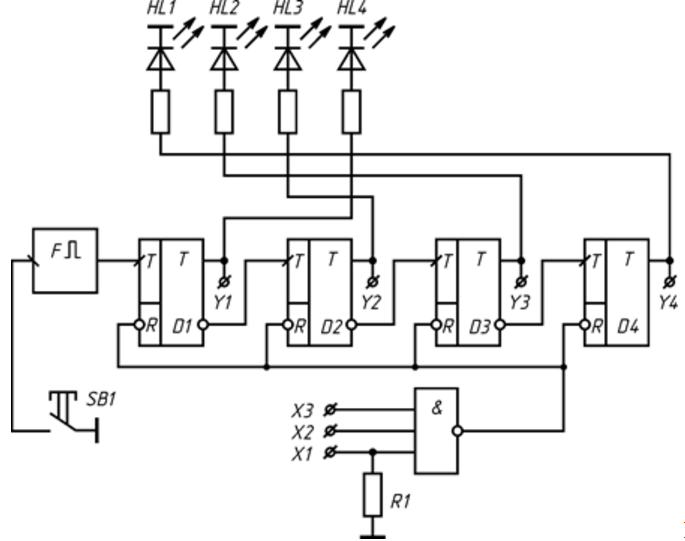

Рассмотрим трехразрядный реверсивный счетчик с последовательным переносом (рис. 3.70).

В режиме вычитания входные сигналы должны подаваться на вход Тв. На вход Тс при этом подается сигнал логического 0. Пусть все триггеры находятся в состоянии 111. Когда первый сигнал поступает на вход Тв, на входе Т первого триггера появляется логическая 1, и он изменяет свое состояние. После этого на его инверсном входе возникает сигнал логической 1.

При поступлении второго импульса на вход Тв на входе второго триггера появится логическая 1, поэтому второй триггер изменит свое состояние (первый триггер также изменит свое состояние по приходу второго импульса). Дальнейшее изменение состояния происходит аналогично. В режиме сложения счетчик работает аналогично 4-разрядному суммирующему счетчику. При этом сигнал подается на вход Тс. На вход Тв подается логический 0. В качестве примера рассмотрим микросхемы реверсивных счетчиков (рис: 3.71) с параллельным переносом серии 155 (ТТЛ):

- ИЕ6 — двоично-десятичный реверсивный счетчик;

- ИЕ7 — двоичный реверсивный счетчик.

Направление счета определяется тем, на какой вывод (5 или 4) подаются импульсы. Входы 1, 9, 10, 15 — информационные, а вход 11 используется для предварительной записи. Эти 5 входов позволяют осуществить предварительную запись в счетчик (предустановку). Для этого нужно подать соответствующие данные на информационные входы, а затем подать импульс записи низкого уровня на вход 11, и счетчик запомнит число.

Вход 14 — вход установки О при подаче высокого уровня напряжения. Для построения счетчиков большей разрядности используются выходы прямого и обратного переноса (выводы 12 и 13 соответственно). С вывода 12 сигнал должен подаваться на вход прямого счета следующего каскада, а с 13 — на вход обратного счета.

Классификация логических элементов

В зависимости от вида используемых сигналов микросхемы с логическим действием бывают:

- Потенциальные: данные на входе представляют собой напряжения различных уровней. Высокое напряжение — это логическая единица, означающая истину. Низкое напряжение называется логическим нулем и считается ложным значением. В зависимости от подачи напряжения на входе и выполненной операции на выходе получается истина или ложь.

- Импульсные: отсутствие импульсов = логический ноль, наличие импульса = логическая единица.

- Импульсно-потенциальные: Наличие положительного импульса заданной амплитуды означает логическую единицу, его отсутствие — логический ноль.

В зависимости от типа используемых материалов выделяют следующие разновидности микросхем:

- Диодно-резисторная логика. Использование схем, разработанных по этой технологии, возможно только с полупроводниковыми триодами. Для самостоятельного применения этих элементов характерны большие потери.

- Диодно-транзисторная логика. Операции при этой технологии реализуются посредством диодных цепей, а усиление и инверсия сигнала происходят благодаря транзистору.

- Резисторно-транзисторная логика. Данный класс чипов базируется на резисторах и биполярных транзисторах.

- Транзисторно-транзисторная логика. За триодом, выполняющим логическую операцию, подключают выходной инвертор для четкости сигнала на выходе.

2 Краткие теоретические сведения

Счётчик – устройство для подсчёта числа входных импульсов.

Параметры счётчика:

- модуль счёта М – число устойчивых состояний;

- ёмкость Е – максимальное число, которое может быть записано в счётчик (Е=М-1);

- быстродействие (скорость перехода из состояния «все 1» в состояние «все 0» и наоборот).

Классификация:

- По направлению счёта:

- суммирующие;

- вычитающие;

- реверсивные;

- По способу построения цепи переноса:

- с последовательным переносом;

- с параллельным переносом;

- с комбинированным переносом;

- По способу переключения триггера:

- синхронные;

- асинхронные.

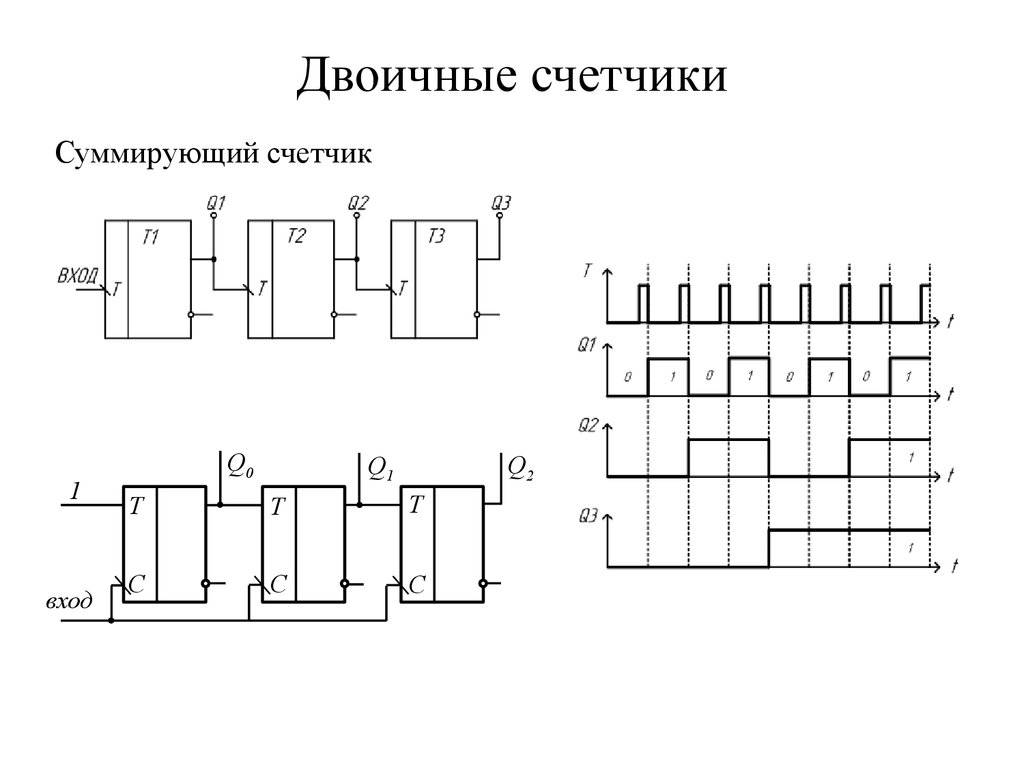

2.1 Простейший суммирующий асинхронный счётчик

Счётчик представляет собой несколько последовательно включенных счётных триггеров. Напомним, что по каждому входному импульсу счётный триггер изменяет своё состояние на противоположное.

Если вход синхроимпульса триггера отмечен как «\», то опрокидывание триггера происходит по заднему фронту, если как «/» – то по переднему.

Для того чтобы разобраться, как работает схема двоичного счётчика, воспользуемся временными диаграммами сигналов на входе и выходах этой схемы, приведёнными на рисунке 2.2.

Пусть первоначальное состояние всех триггеров счётчика будет нулевым. Это состояние мы видим на временных диаграммах. Запишем его в таблицу 2.1. После поступления на вход счётчика тактового импульса (который воспринимается по заднему фронту) первый триггер изменяет своё состояние на противоположное, то есть единицу.

Запишем новое состояние выходов счётчика в ту же самую таблицу. Так как по приходу первого импульса изменилось состояние первого триггера, то этот триггер содержит младший разряд двоичного числа (единицы).

Таблица 2.1 – Изменение уровней на выходе суммирующего двоичного счётчика при поступлении на его вход импульсов

| Номер входного импульса | Q2 | Q1 | Q0 |

| 1 | 1 | ||

| 2 | 1 | ||

| 3 | 1 | 1 | |

| 4 | 1 | ||

| 5 | 1 | 1 | |

| 6 | 1 | 1 | |

| 7 | 1 | 1 | 1 |

| 8 |

Подадим на вход счётчика ещё один тактовый импульс. Значение первого триггера снова изменится на прямо противоположное. На этот раз на выходе первого триггера, а значит и на входе второго триггера сформируется задний фронт. Это означает, что второй триггер тоже изменит своё состояние на противоположное. Это отчётливо видно на временных диаграммах, приведённых на рисунке 2.2. Запишем новое состояние выходов счётчика в таблицу 2.1. В этой строке таблицы образовалось двоичное число 2. Оно совпадает с номером входного импульса.

Продолжая анализировать временную диаграмму, можно определить, что на выходах приведённой схемы счётчика последовательно появляются цифры от 0 до 7. Эти цифры записаны в двоичном виде. При поступлении на счётный вход счётчика очередного импульса, содержимое его триггеров увеличивается на 1. Поэтому такие счётчики получили название суммирующих двоичных счётчиков. Если информацию снимать с инверсных выходов триггеров, то получится вычитающий счётчик.

2.2 Простейший вычитающий асинхронный счётчик

Рассмотрим схему счётчика на триггерах, опрокидывающихся по переднему фронту входных импульсов рисунок 2.3

Из временной диаграммы видим, что получился вычитающий счётчик. Если информацию снимать с инверсных выходов триггеров, то получится суммирующий счётчик.

2.3 Счётчик с произвольным модулем счёта

Для построения такого счётчика можно использовать двоичный счётчик, у которого модуль счёта М должен быть больше модуля счёта разрабатываемого счётчика с произвольным модулем счёта.

Пусть нужно сделать счётчик с М= 10.

У 4-х разрядного счётчика модуль счёта равен 16 (больше 10).

Схема счётчика представляет собой 4 последовательно включённых счётных триггера, у которых есть вход сброса R.

Число 10 в двоичной системе счисления представляется 1010. Когда на выходах счетчика будет код 1010, на выходе элемента «И» появится логическая единица, которая запустит схему гашения. Длительность импульса на выходе схемы гашения должна быть достаточна для надёжного сброса всех триггеров счётчика в 0. Разряды числа 1010, равные 1 подаются на схему «И» с прямых выходов триггеров, а равные 0 – с инверсных. Таким образом, как только счётчик досчитает до 10, произойдёт обнуление всех триггеров и счёт продолжится с кода 0000.

Рассмотрим счётчик с М=11 на основе двоичного счётчика в одной микросхеме (без инверсных выходов).

1110=10112

В качестве схемы гашения может быть RS-триггер.

В этой схеме М=100012 = 1710

Сигнал на входе К счётчика будет действовать в течение одного периода входных импульсов

Параметры механизмов учета нового типа

Если возникла необходимость замены стандартных приборов учета на автоматические, нужно знать определенные нюансы. Именно они будут влиять на качество прибора и его долговечность:

- Материал корпуса, проверенный временем, это латунь или бронза. В крайнем случае — нержавеющая сталь.

- Цвет корпуса. Как правило, для холодной и горячей воды они разные. Синий для холодной воды — красный для горячей. Универсальные приборы серого цвета.

- Гарантийный срок такой же, как и на обычные механические приборы учета. Шесть лет на холодную воду и четыре года на горячую.

- Класс точности. Градация метрологической погрешности есть в паспорте изделия. Различают четыре класса точности A, B, C, D. Приборы класса «А» — самые простые. Соответственно класс «D» — высокоточные, но и самые дорогие приборы учета.

Если подобран качественный водомер, он будет обладать большим сроком эксплуатации. А это от 10 до 2 лет. Что для холодной воды это два поверочных промежутка.

Синхронизирующие устройства

Синхронизирующие устройства определяют порядок работы и взаимодействие узлов и систем преобразователя. Наиболее простыми и распространенными являются схемы с трансформаторами (рис. 8, а). На первичные обмотки трехфазного трансформатора подаются напряжения управления со сдвигом 120°.

Рис. 8. Синхронизирующее устройство и векторная диаграмма выходных напряжений

Импульсы снимаются со вторичных обмоток и представляют собой напряжения между концами обмоток и нулевым проводом. Каждый тиристор может быть открыт одну треть периода и работает по одной шестой периода с двумя тиристорами второй группы (например, 4-й — с 3-м и 5-м).

Импульсы тиристоров одной группы сдвигаются на 120°, концы вторичных обмоток соединяются с управляющими векторами тиристоров согласно векторной диаграмме выходных напряжений (рис. 8, б). Вентили в цепи тока управления предохраняют тиристоры от возникновения отрицательного потенциала на управляющем электроде и от короткого замыкания между фазами переменного напряжения, которое подается на управляемый мост.

Для синхронизации импульсов используется точка перехода напряжения или тока через нуль. Эти точки имеют сдвиг 180° независимо от степени искажения формы кривой напряжения или тока. Схемы, вырабатывающие импульсы в момент перехода напряжения или тока через нуль, называются нуль-органами.

На рис. 9, а показаны нуль-орган с использованием логического элемента ИЛИ — НЕ. Напряжение Uвх на вторичной обмотке трансформатора преобразуется в два напряжения Uвх1 и Uвх2, находящихся в противофазе (рис. 9, б), так как одно напряжение направлено от конца обмотки к нулевой точке, а другое — наоборот. В каждый полупериод эти напряжения создают ток через стабилитроны Ст1 и Ст2.

Рис. 9. Нуль-орган с использованием логических элементов ИЛИ-НЕ

Напряжение стабилизации стабилитронов ограничивается напряжением Uогр. Резисторы R1 и RЗ служат добавочными и совместно со стабилитронами создают схемы стабилизации напряжения. Каждый полупериод стабилизированное напряжение подается на вход транзистора Т. Резисторы R2 и R4 ограничивают базовый ток транзистора.

Напряжение стабилизации выбирается больше напряжения смещения Еб, и транзистор открыт большую часть полупериода. В момент перехода напряжения через нуль напряжение смещения закрывает транзистор и на выходе возникает импульс Uвых, примерно равный напряжению питания Ек. Функцию ИЛИ – НЕ осуществляет транзистор в схеме. Если напряжение входа больше напряжения смещения Uвх > Еб, импульса нет, если Uвх меньше Еб — импульс есть. Для синхронизации работы многофазного выпрямителя такая схема должна быть включена в каждую фазу.

D – триггеры.

Для использования триггеров в реальных счетных устройствах, необходимо иметь

возможность дополнительного управления их состояниями – предустановки, обнуления, активации с помощью

счетного тактового импульса.

Что бы осуществить эту операцию в схему счетного триггера добавляется еще три входа.

PRESET(PR) – восстанавливает на выходе триггера состояние 1, а СLEAR(CL) – состояние 0.

С помощью тактового входа Т осуществляется общая синхронизация триггера, относительно

других элементов схемы счетного устройства.

Импульс поступающий на счетный вход D меняет состояние триггера, только при наличии 1 на

тактовом входе.

Логические схемы “И” на диодах

Схема И может быть собрана на диодах (рис. 2, б, в). Принцип построения схемы основан на том, что при наличии сигнала 0 хотя бы на одном входе сигнал 0 передается со входа на выход через открытый диод и обеспечивает запирание диодов, на входах которых действуют сигналы 1.

Рис. 2. Схема И на диодах

На рис. 2, б приведена схема для положительной логики. Сигнал 0 (ен) по абсолютной величине больше сигнала 1 (ев). Если на вход В подается сигнал 0, например 10 В, а на входах А и С действуют сигналы 1, например 2, то открытым окажется диод с наиболее низким потенциалом катода, т.е. диод, присоединенный ко входу В, а два других диода будут закрыты. Напряжение сигнала 0 (10 В) выделяется на резисторе Rн, с которого снимается сигнал выхода.

На рис. 2, в приведена схема И для отрицательной логики. Здесь сигнал 0 также по абсолютному значению больше сигнала 1, однако сигналы – положительные, поэтому полярность напряжения сигналов на входах изменена. При наличии сигнала 0 на входе В и сигналов 1 на остальных входах открыт диод, присоединенный ко входу В. Два других диода закрыты высоким положительным потенциалом на катодах. На выходе возникает сигнал — 0. При наличии сигналов 1 на всех входах все диоды открыты и на выходе – сигнал 1.

Асинхронные счётчики

Данные типы счётчиков состоят из цепочёк JK-триггеров, которые работают в счётном режиме, когда выход предыдущего триггера служит входом для следующего. В такой схеме триггеры включаются последовательно, а, следовательно, и выходы счётчика также переключаются последовательно, один за другим (отсюда второе название асинхронных счётчиков – последовательные счётчики). Так как переключение разрядов происходит с некоторой задержкой, поэтому и сигналы на выходах счётчика появляются не одновременно с входным сигналом и между собой, то есть асинхронно.

Микросхемы асинхронных счётчиков применяются не очень часто, в качестве примера можно привести микросхемы типа ИЕ2 (четырёхразрядный двоично-десятичный счётчик), ИЕ5 (четырёх разрядный двоичный счётчик) и ИЕ19 (сдвоенный четырёхразрядный счётчик).

Асинхронные счётчики: слева направо ИЕ2, ИЕ5, ИЕ19.

Данные типы счётчиков имеют входы сброса в нуль (вход R), вход установки в 9 (вход S у ИЕ2), счётный или тактовый вход (вход С) и выходы, которые могут обозначаться как номера разрядов (0, 1, 2, 4) или как вес каждого разряда (1, 2, 4, 8).

Микросхема К555ИЕ2 относится к двоично-десятичным счётчикам, то есть счёт у неё идет от 1 до 9, а потом выводы обнуляются и счёт идёт сначала. Внутренне данный счётчик состоит из четырёх триггеров, которые разделены на две группы: один триггер (вход С1, выход 1) и три триггера (вход С2, выходы 2, 4, 8). Такая внутренняя организация позволяет значительно расширить применение данного типа микросхемы, например данную микросхему можно использовать в качестве делителя на 2, на 5 или на 10. Счётчик ИЕ2 имеет два входа для сброса в нуль объединенных по И, а так же два входа для установки в 9 тоже объединённых по И.

Для реализации счёта необходимо сбросить счётчик подачей на входы R высокого логического уровня, а на один из входов S сигнал низкого уровня. В таком режиме счётчик будет «обнулён» и последовательный счёт заблокирован. Чтобы восстановить функцию счета необходимо установить на входы R низкий уровень сигнала.

Для организации делителя на 2 необходимо подавать сигнал на С1, а снимать с выхода 1; делитель на 5 подавать сигнал на С2, а снимать с выхода 8; делитель на 10 выход 8 соединяют с С1, сигнал подают на С2, а снимают с выхода 1.

Микросхема К555ИЕ5 представляет собой двоичный счётчик, в отличие от ИЕ2 считает до 16 и сбрасывается в нуль. Также как и ИЕ2 состоит из двух групп триггеров со входами С1 и С2, а выходы 1 и 2,4,8. В отличии от ИЕ2 имеет только два входа сброса в нуль, а входов установки нет.

Микросхема К555ИЕ19 практически идентична двум микросхемам К555ИЕ5 и представляет собой два чётырёхразрядных двоичных счётчика, каждый счётчик имеет свой счётный вход С и вход сброса R. Если объединить выход 8 первого счётчика и вход С второго счётчика, то можно получить восьмиразрядный двоичный счётчик.

Краткие теоретические сведения

Триггеры предназначены для запоминания двоичной информации. Использование триггеров позволяет реализовывать устройства оперативной памяти (то есть памяти, информация в которой хранится только на время вычислений).

Однако триггеры могут использоваться и для построения некоторых цифровых устройств с памятью, таких как счётчики, преобразователи последовательного кода в параллельный или цифровые линии задержки.

RS-триггер

Основным триггером, на котором базируются все остальные триггеры является RS-триггер. RS-триггер имеет два логических входа:

- R – установка 0 (от слова reset);

- S – установка 1 (от слова set).

RS-триггер имеет два выхода:

- Q – прямой;

- Q- обратный (инверсный).

Состояние триггера определяется состоянием прямого выхода. Простейший RS-триггер состоит из двух логических элементов, охваченных перекрёстной положительной обратной связью.

Рассмотрим работу триггера:

Пусть R=0, S=1. Нижний логический элемент выполняет логическую функцию ИЛИ-НЕ, т.е. 1 на любом его входе приводит к тому, что на его выходе будет логический ноль Q=0. На выходе Q будет 1 (Q=1), т.к. на оба входа верхнего элемента поданы нули (один ноль – со входа R, другой – с выхода ). Триггер находится в единичном состоянии. Если теперь убрать сигнал установки (R=0, S=0), на выходе ситуация не изменится, т.к. несмотря на то, что на нижний вход нижнего логического элемента будет поступать 0, на его верхний вход поступает 1 с выхода верхнего логического элемента.

Триггер будет находиться в единичном состоянии, пока на вход R не поступит сигнал сброса. Пусть теперь R=1, S=0. Тогда Q=0, а =1. Триггер переключился в “0”. Если после этого убрать сигнал сброса (R=0, S=0), то все равно триггер не изменит своего состояния. Для описания работы триггера используют таблицу состояний (переходов). Обозначим:

- Q(t) – состояние триггера до поступления управляющих сигналов (изменения на входах R и S);

- Q(t+1) – состояние триггера после изменения на входах R и S.

Таблица переходов RS триггера в базисе ИЛИ-НЕ

| R | S | Q(t) | Q(t+1) | Пояснения |

| Режим хранения информации R=S=0 | ||||

| 1 | 1 | |||

| 1 | 1 | Режим установки единицы S=1 | ||

| 1 | 1 | 1 | ||

| 1 | Режим установки нуля R=1 | |||

| 1 | 1 | |||

| 1 | 1 | * | R=S=1 запрещённая комбинация | |

| 1 | 1 | 1 | * |

RS-триггер можно построить и на элементах “И-НЕ” (рисунок 2.2).

Входы R и S инверсные (активный уровень “0”). Переход (переключение) этого триггера из одного состояния в другое происходит при установке на одном из входов “0”. Комбинация R=S=0 является запрещённой.

Таблица переходов RS триггера в базисе “2И-НЕ”

| R | S | Q(t) | Q(t+1) | Пояснения |

| * | R=S=0 запрещённая комбинация | |||

| 1 | * | |||

| 1 | Режим установки нуля R=0 | |||

| 1 | 1 | |||

| 1 | 1 | Режим установки единицы S=0 | ||

| 1 | 1 | 1 | ||

| 1 | 1 | Режим хранения информации R=S=1 | ||

| 1 | 1 | 1 | 1 |

Синхронный RS-триггер

Схема RS-триггера позволяет запоминать состояние логической схемы, но так как при изменении входных сигналов может возникать переходный процесс (в цифровых схемах этот процесс называется “опасные гонки”), то запоминать состояния логической схемы нужно только в определённые моменты времени, когда все переходные процессы закончены, и сигнал на выходе комбинационной схемы соответствует выполняемой ею функции. Это означает, что большинство цифровых схем требуют сигнала синхронизации (тактового сигнала).

Все переходные процессы в комбинационной логической схеме должны закончиться за время периода синхросигнала, подаваемого на входы триггеров. Триггеры, запоминающие входные сигналы только в момент времени, определяемый сигналом синхронизации, называются синхронными. Принципиальная схема синхронного RS триггера приведена.

Таблица переходов синхронного RS-триггера

| R | S | C | Q(t) | Q(t+1) | Пояснения |

| 1 | Режим хранения информации R = S = 0 | ||||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | Режим установки единицы S =1 | ||

| 1 | 1 | 1 | 1 | ||

| 1 | 1 | Режим установки нуля R=1 | |||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | * | R = S = 1 запрещённая комбинация | |

| 1 | 1 | 1 | 1 | * |

В таблице 2.3. под сигналом С подразумевается синхроимпульс. Без синхроимпульса синхронный RS триггер сохраняет своё состояние.

Логические схемы “ИЛИ” на диодах

Моделью схемы ИЛИ может служить цепь, изображенная на рис. 4, а. Лампа загорится, если замкнуты контакты Р1, «ИЛИ» Р2, «ИЛИ» Р3.

Рис. 4. Схема ИЛИ на диодах

На выходе схемы ИЛИ возникает сигнал 1, если такой же сигнал подан на один или несколько входов. Схема ИЛИ является схемой сборки (информации); по какому бы каналу ни пришел сигнал 1, он появляется на выходе. Схема ИЛИ осуществляет логическое сложение, что подтверждается выражением:

Действительно, у = 0 при х1 = х2 = … = хn = 0; у = 1, если на одном входе возникает сигнал 1, а на всех других — сигнал 0; у = 1 при х1 = х2 = … = xn = 1 (следует помнить, что у и х могут иметь только два значения 1 или 0). Логическое сложение носит название дизъюнкции, поэтому схему можно назвать дизъюнктором.

Схема ИЛИ может быть собрана на диодах в варианте для положительной логики (Рис. 4, б) и для отрицательной логики (рис. 4, в). Принципы действия этих схем и логических схем И на диодах ничем не отличаются. При перемене уровня сигналов 1 и 0 схема ИЛИ может выполнять функции схемы И.

Что такое логические элементы

Логические элементы представляют собой устройства, которые могут быть реализованы на электронной полупроводниковой базе. Они выполняют некоторую логическую функцию преобразования входного сигнала. На нескольких простых логических элементах можно построить сколь угодно много сложных устройств, например регистров, сумматоров, счетчиков импульсов.

Для описания работы различных электронных устройств удобно использовать элементы алгебры логики, которая, как известно, работает с переменными, принимающими только два значения 1 и 0, то есть включено или выключено.

Определение количества логических элементов, которые можно построить на базе двоичной логики, выполняется по формуле 24, то есть составляет 16.

Устройство аппарата

Прибор представляет собой электронно-вычислительную технику, со встроенными датчиками импульсов (действий, циклических повторов механического типа).

Устройство имеет цифровой дисплей, на котором отображается количество обработанной информации по подсчету импульсов и команд.

Импульсами считается выход единицы готовой продукции, завершение цикла производственных машин, поступление энергетического ресурса (в установленных единицах измерения).

Производители предлагают также комбинированные цифровые приборы, с расширенными возможностями и увеличенным рабочим диапазоном.